Synchronization Hardware, 하드웨어 동기화

Critical Section Problem의 경우 단일 처리기 환경에서는 저번 포스팅의 얘기했던 알고리즘과 같이 Interrupt를 방지함으로써

간단하게 해결할 수 있다. 하지만 이는 다중 처리기 환경의 경우에는 적용할 수 없다.

다중 처리기 환경에서는 인터럽트가 안 된다는 메시지를 모든 처리기에 전달해야 하기 때문에 시간이 오래 걸리며

또한 메시지를 확인하기 위해서 Critical Section에 들어가는 것을 지연시키기 때문에 비효율적이다.

그렇기 때문에 많은 Hardware들이 특별한 하드웨어 명령어들을 제공하고 있다.

이번 포스팅에서는 그 중에서 가장 대표적인 Test-and Set 명령어를 알아보도록 하자.

Test-and Set을 코드로 표현하면 위와 같다. 구조는 간단하다. target변수를 true로 변환하고 이전 값을 반환한다.

이때 중요한 점은 taret을 true로 바꾸는 연산의 Atomicity를 보장해야 한다는 것이다.

즉, 해당 연산은 Interrupt가 걸려서는 안 된다는 것이다. 그럼 Test-and Set명령어를 사용한 코드를 살펴보자.

처음에 lock변수는 false로 초기화 되어 있다. 처음 TestAndSet함수에 lock이 들어가면 false가 리턴되며

그 다음부터는 계속해서 true가 리턴된다. 이로써 만일 두 개의 처리기에서 Test-and Set명령어가 동시에 실행되도

이들은 임의의 순서로 처리되게 되므로 Mutual Exclusion이 성립하게 된다. 특정 처리기가 들어와 lock을 true로 변경시키면

Lock은 false로 변경시키기 전까지 계속해서 true로 유지되는 것이다.

하지만 위의 설명했듯이 임의의 순서로 실행되기 때문에 특정 처리기의 경우 계속해서 순서가 밀릴 수 있다.

즉, Bounded Waiting이 성립하지 않는 것이다. 때문에 이 점을 고려해서 코드를 수정해야 한다.

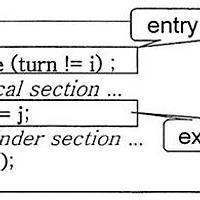

위 코드를 살펴보면 Test-and-Set연산을 통해서 한번의 하나의 처리기만 Critical Section으로의 진입이 허가된다.

그 뒤 나머지 연산자를 통해서 반복문을 돌게 되는데 이때 j와 i의 값이 같아 질 때까지 돈다는 것은 아무도 진입하려

하지 않았다는 것이므로 lock을 false로 돌리고 끝난다.하지만 중간의 한 처리기가 진입을 요구했다면

해당 처리기의 waiting문을 false로 변경시켜서 첫 번째 반복문을 통과하게 만들어 준다.

이로써 Critical Section해결 방안의 3가지 조건을 모두 만족하게 되는 것이다.

'C.E > OS' 카테고리의 다른 글

| CCL @ KEY (0) | 2013.12.22 |

|---|---|

| Deadlock (0) | 2013.12.09 |

| Process Synchronization - Critical Section Problem (0) | 2013.12.09 |

| Process Synchronization - Process Synchronization (0) | 2013.12.09 |

| CPU Scheduling - Scheduling Algorithm_6 (0) | 2013.12.09 |