DMA(Direct Memory Access) structure

주변장치의 데이터는 Device controller에 의해 Local buffer로 이동한다.

그러나 전송할 데이터가 많은 경우, 많은 양의 데이터의 이동으로 인한 부담이 커지게 된다.

Device controller가 데이터의 한 블록을 이동시키는데 이 과정에서 DMA로 인해

CPU의 개입이 필요없게 된다. CPU에서는 데이터 이동이 완료되었다는 단 한번의 Interrupt만 발생한다.

데이터가 전송되는 동안 CPU는 다른 작업을 수행할 수 있게 되어 효율성이 높아진다.

근데 만일 CPU와 DMA가 동시에 버스를 사용하고자 할 떄 속도가 느린 DMA는

속도가 빠른 CPU에게 밀려 계속 버스를 사용할 수 없는 starvarion상태에 빠지게 된다.

그래서 CPU가 DMA에게 버스의 사용권을 양보하는데 이를 Cycle Stealing이라고 한다.

1. DMAC(DMA Controller)가 Memory Cycle Request 신호를 요청

2. CPU는 요청을 받으면 메모리의 다음 사이클을 제공(CPU는 한 사이클 동안 대기 상태)

Cycle Stealing을 통해서 DMA가 기아상태에 빠지는 것을 막을 수 있다. 하지만

DMA는 Cycle Stealing을 위해 한번, 그리고 데이터의 전송을 위해 한번. 이렇게

데이터를 전송할 때 마다 시스템 버스를 두번이용하게 된다.

'C.E > OS' 카테고리의 다른 글

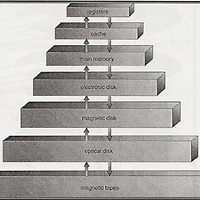

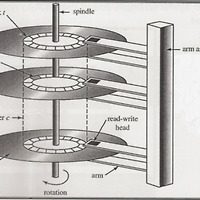

| Storage Structure - Storage Hierarchy (0) | 2013.11.15 |

|---|---|

| Storage Structure - Main&Cache&Secondary (0) | 2013.11.15 |

| I/O Structure - Synchronous&Asynchronous (0) | 2013.11.15 |

| Computer Structure - 기본 구조 (0) | 2013.11.15 |

| Computer Structure - 폰 노이만 컴퓨터(Von Neumann Machines) (0) | 2013.11.15 |